奈米電子研究中心愛美科(IMEC)與益華電腦(Cadence Design Systems)日前共同宣布,採用極紫外光微影製程(EUV)與193浸潤式(193i)微影技術完成首款5奈米測試晶片的設計定案(Tape Out)。

IMEC製程技術開發資深副總裁An Steegen表示,在推展世界上最先進的5奈米甚至更小的製程中,雙方的合作扮演重要的角色,共同開發出先進製程技術,如此款測試晶片。Cadence的平台不但易於使用,也有助工程團隊高效率地開發先進製程所需的規則(Rule Set)。

Cadence數位Signoff事業群資深副總裁暨總經理Anirudh Devgan指出,此次合作成功可證明Cadence與IMEC持續致力於將曝光技術應用至越來越多更小的製程。透過IMEC技術與Cadence Innovus設計實現系統所建立的工作流程,為開發創新的次世代行動與電腦先進製程設計奠定基礎。

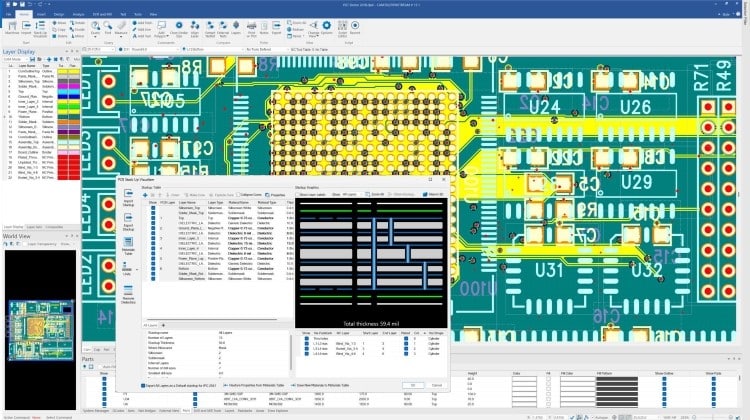

為了生產此測試晶片,IMEC與Cadence將設計規則、資料庫以及布局繞線技術進行最佳化,透過Cadence Innovus設計實現系統獲得最佳功率、效能與面積(PPA)。IMEC和Cadence利用EUV搭配自動對準四重曝光(SAQP)和193i光源成功完成處理器設計定案,其中將金屬間距由原先的32奈米縮短為24奈米,把顯影技術推至極限。

Innovus設計實現系統為一次世代實體設計實現解決方案,讓系統晶片(SoC)開發人員得以提供最佳PPA設計,同時加速上市前置時間。Innovus設計實現系統由大規模平行架構與突破性的最佳化技術所驅動,一般可提升10至20%的PPA,同時可將整體流程速度與產能最高提高10倍。